J-K

FLIP-FLOP DAN TOGGLE FLIP-FLOP (T FLIP-FLOP)

a.

Mengetahui apa itu J-K Flip-Flop dan Toggle Flip-Flop (T Flip-Flop)

b.

Mengetahui bentuk rangkaian J-K Flip-Flop dan Toggle Flip-Flop (T Flip-Flop)

Alat:

1. Power supply

2. Ground

Berfungsi sebagai penghantar arus listrik langsung ke

bumi atau tanah.

Bahan:

1. Gerbang

NAND

Spesifikasi IC 7400:

·Tegangan Suply: 7 V

·Tegangan input: 5.5 V

·Beroperasi pada suhu udara 0 sampai +70 derjat

·Kiasaran suhu penyimpanan: -65 derjat sampai 150 derjat

celcius

Konfiugurasi pin:

-Vcc: Kaki 14

- GND: Kaki 7

-Input: Kaki 1 dan 2, 4 dan 5, 13 dan 12, 10 dan 9

- Output: Kaki 3, 6, 1

2. Inverter (NOT)

1. Gerbang

NAND

Gerbang

NAND adalah gabungan gerbang NOT dan AND mempunyai dua atau lebih sinyal

masukan (input) tetapi hanya satu sinyal keluaran (output). IC 7400

merupakan ic yang dibangun dari gerbang logika dasar NAND. Gerbang NAND

menghendaki semua inputnya bernilai 0 (terhubung dengan ground) atau salah

satunya bernilai 1 agar menghasilkan output yang berharga 1.

2. Inverter

(NOT)

Inverter atau pembalik(NOT) adalah suatu gerbang yang bertujuan untuk menghasilkan logika output kebalikan dari logika input. Adapun simbol dan tabel kebenaran gerbang Inverter seperti berikut:

3.

Materi

10.5 J-K

Flip-Flop

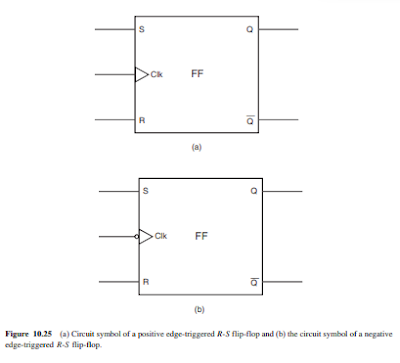

Flip flop J-K berperilaku dengan cara yang sama seperti Flip flop

R-S kecuali salah satu entri dalam tabel fungsi. Dalam kasus flip-flop

R-S, kombinasi input S = R = 1 (dalam kasus flip-flop dengan input HIGH aktif)

dan kombinasi input S = R = 0 (dalam kasus sandal jepit dengan input LOW aktif)

dilarang. Dalam kasus flip-flop J-K dengan input HIGH aktif, output dari toggle

flip-flop, yaitu, ia pergi ke keadaan lain, untuk J = K = 1 . Output

bolak-balik untuk J = K = 0 dalam kasus Flip flop yang memiliki input LOW

aktif. Dengan demikian, Flip flop J-K mengatasi kombinasi input terlarang

dari sandal jepit R-S. Gambar masing-masing 10.26(a) dan (b) tampilkan simbol

sirkuit Flip flop J-K yang dipicu level dengan input LOW aktif DAN TINGGI

aktif, bersama dengan tabel fungsinya. Gambar 10.27 menunjukkan realisasi Flip

flop J-K dengan R-S Flip-flop.

Tabel karakteristik untuk Flip flop J-K dengan input HIGH J dan K

aktif dan Flip flop J-K dengan input LOW J dan K aktif masing-masing

ditampilkan dalam Buah Ara 10.28(a) dan (b) Peta Karnaugh ditampilkan dalam

Gbr. 10.28 (c) untuk tabel karakteristik Gbr. 10.28(a) dan di Gbr. 10.28(d)

untuk tabel karakteristik Gbr. 10.28 (b). Persamaan karakteristik untuk

Karnaugh peta Buah Ara 10.28(c) dan (d) masing-masing

10.5.1

J-K Flip-Flop with PRESET and CLEAR Inputs

Seringkali perlu untuk menghapus Flip flop ke status logika '0' (Qn

= 0) atau membuatnya ke status logika '1' (Qn = 1). Contoh bagaimana hal ini

diwujudkan ditunjukkan dalam Gbr. 10.29(a). Flip flop dibersihkan

(artinya, Qn = 0) setiap kali input CLEAR adalah '0' dan input PRESET adalah

'1'. Flip flop telah ditetapkan ke logika '1' menyatakan setiap kali

input PRESET adalah '0' dan input CLEAR adalah '1'. Di sini, CLEAR dan Input

PRESET aktif saat LOW. Gambar 10.29(b) menunjukkan simbol sirkuit dari

presettable ini, jelas, jam J-K flip-flop. Gambar 10.29(c) memperlihatkan tabel

fungsi dari Flip flop tersebut. Hal ini terbukti dari tabel fungsi yang,

setiap kali input PRESET aktif, output masuk ke '1' terlepas dari status jam,

input J dan K. Demikian pula, ketika Flip flop dibersihkan, yang adalah,

input CLEAR aktif, output masuk ke status '0' terlepas dari status jam, J dan

input K. Dalam sandal jepit jenis ini, input PRESET dan CLEAR tidak boleh dibuat

aktif pada saat yang sama.

10.5.2

Master–Slave Flip-Flops

Setiap

kali lebar denyut nadi clocking sandal jepit lebih besar dari penundaan

perambatan flip-flop, perubahan keadaan pada output tidak dapat diandalkan.

Dalam kasus sandal jepit yang dipicu tepi, ini lebar pulsa akan menjadi lebar

denyut pemicu yang dihasilkan oleh bagian detektor tepi flip-flop dan bukan

lebar denyut nadi sinyal jam input. Fenomena ini disebut sebagai perlombaan

Masalah. Karena keterlambatan perambatan biasanya sangat kecil, kemungkinan

terjadinya kondisi balapan cukup tinggi. Salah satu cara untuk mengatasi

masalah ini adalah dengan menggunakan master-slave Konfigurasi. Gambar 10.30(a)

menunjukkan flip-flop master-budak yang dibangun dengan dua flip-flop J-K.

flip-flop pertama disebut master flip-flop dan yang kedua disebut budak. Jam ke

flip-flop budak adalah pelengkap jam untuk master flip-flop. Ketika jam

berdenyut hadir, master flip-flop diaktifkan sementara budak flip-flop

dinonaktifkan. Akibatnya, master flip-flop dapat mengubah keadaan sementara

budak flip-flop tidak bisa. Ketika jam berjalan RENDAH, master flip-flop akan

dinonaktifkan sementara flip-flop budak diaktifkan. Oleh karena itu, budak J-K

flip-flop berubah status sesuai status logika pada input J dan K-nya. Isi dari

master flip-flop oleh karena itu ditransfer ke flip-flop budak, dan master

flip-flop, dinonaktifkan, dapat memperoleh input baru tanpa mempengaruhi

output. Seperti yang akan jelas dari deskripsi di atas, master - flip-flop

budak adalah flip-flop yang dipicu denyut nadi dan bukan yang dipicu tepi.

Gambar 10.30(b) menunjukkan tabel kebenaran flip-flop J-K master-slave dengan

input LOW PRESET dan CLEAR aktif dan input HIGH J dan K aktif. Konfigurasi

master-slave telah usang. IC yang lebih baru teknologi seperti 74LS, 74AS,

74ALS, 74HC dan 74HCT tidak memiliki flip-flop master-budak di Seri.

10.6

Toggle Flip-Flop (T Flip-Flop)

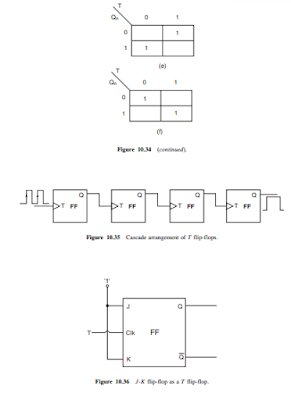

Output

dari flip-flop bolak-balik, juga disebut T flip-flop, mengubah status setiap

kali dipicu pada input T-nya, yang disebut input bolak-balik. Artinya, output

menjadi '1' jika '0' dan '0' jika itu '1'. Gambar masing-masing 10.34(a) dan

(b) menunjukkan simbol sirkuit yang dipicu tepi positif dan negate flip-flop T

yang dipicu tepi, bersama dengan tabel fungsinya.

Jika kita

menganggap input T aktif saat HIGH, tabel karakteristik flip-flop tersebut

ditampilkan dalam Gbr. 10.34 (c). Jika input T aktif saat RENDAH, maka tabel

karakteristik akan seperti yang ditunjukkan dalam Gbr. 10.34(d). Peta Karnaugh

untuk tabel karakteristik Buah Ara 10.34(c) dan (d) ditampilkan dalam Buah Ara

masing-masing 10,34(e) dan (f). Persamaan karakteristik seperti yang ditulis

dari peta Karnaugh adalah sebagai berikut:

Hal ini

jelas dari prinsip operasional flip-flop T bahwa frekuensi sinyal di Output Q adalah

setengah dari frekuensi sinyal yang diterapkan pada input T. Pengaturan

bertingkat nT flip-flop, di mana output dari satu flip-flop terhubung ke input

T dari flip-flop berikut, dapat digunakan untuk membagi frekuensi sinyal input

dengan faktor 2n. Gambar 10.35 menunjukkan pembagian-oleh-16 sirkuit yang

dibangun di sekitar pengaturan bertingkat empat flip-flop T.

10.6.1

J-K Flip-Flop sebagai Flip-Flop Toggle

Jika kita

ingat tabel fungsi sandal jepit J-K, kita akan melihat bahwa, ketika J dan K

input flip-flop terikat ke level aktif mereka ('1' jika J dan K aktif saat

HIGH, dan '0' level ketika J dan K aktif ketika LOW), flip-flop berperilaku

seperti flip-flop al jepit, dengan input jamnya melayani sebagai input T.

Bahkan, flip-flop J-K dapat digunakan untuk membangun sandal jepit lainnya.

Itulah sebabnya juga kadang-kadang disebut sebagai flip-flop universal. Gambar

10.36 menunjukkan penggunaan flip-flop J-K sebagaiT flip-flop.

·

Buka aplikasi proteus

·

Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan

komponen Gerbang nand, not, jkff, clock, logic state, logic probe, 4013

·

Rangkai setiap komponen menjadi rangkaian yang diinginkan

·

Ubah spesifikasi komponen sesuai kebutuhan

·

Jalankan simulasi rangkaian.

|

Prinsip kerja:

Gambar

(10.24 a): Ketika input berlogika 1 maka akan masuk ke gerbang not sehingga

keluarannya menjadi 0, lalu akan menjadi input bagi gerbang nand, selain itu

input lainnya juga berlogika 1 sehingga output akhirnya berlogika 0, begitu

pula jika input awal berlogika 0, maka output akhir juga berlogika 1.

Gambar 10.24 b: Gerbang yang di gunakan adalah gerbang and, ketika input berlogika 0 maupun 1 maka output yang dikeluarkan berlogika 1, gerbang and disini mempunyai input aktif rendah.

Gambar (10.26 a dan b): Pada gambar 10.25 a clocknta aktif tinggi sedangkan dibawah aktif rendah. Jika r berlogika 1 dan s berlogika 0 maka q akan berlogika 0 dan q komplemen berlogika 1. Namun, jika r berlogika 0 dan s berlogika 1 maka q akan berlogika 0 dan q komplemen 1.

Gambar (10.27): ketika kedua input atau salah satu berlogika 1 maka q dan -q

akan mengeluarkan output 0 dan 1, kalau dua dua input berlogika 0 maka q

dan -q mengeluarkan output 1.

Gambar (10.29 a): ketika kedua input atau salah satu berlogika 0 maka q dan -q akan

mengeluarkan output 0 dan 1 atau sebaliknya, namun jika dua dua input berlogika

1 maka q dan -q mengeluarkan output beralih-alih.

Gambar

(10.29 b): pada gambar 10.29 b r dan s aktif

rendah, untuk prinsip bisa dilihat oleh

tabel berikut

Gambar (10.31): ketika kedua input atau salah satu berlogika 0 maka q dan -q akan

mengeluarkan output 0 dan 1 atau sebaliknya, namun jika dua dua input berlogika

1 maka q dan -q mengeluarkan output beralih-alih.

Gambar (10.32): Pada gambar b ketika input berlogika 0 atau 1 maka outputnya menjadi

beralih alih, pada gambar c jika inputnya 1 atau 0 maka outputnya tetap 0.

Gambar

10.34: Pada gambar kali ini digunakan t flip

flop, t flip lop disini dibuat dengan menggunakan d ff dan jk ff, dikarenakan t

ff tidak tersedia di proteus. gambar diatas merupakan t flipflop aktif tinggi

dan yang dibawahnya t ff aktif rendah. ketika dijalankan

maka output yang dihasilkan akan berubah" atau beralih". untuk lebih jelasnya bisa

dilihat di tabel kebenaran

Gambar

10.35: pada gambar kali ini digunakan t flip

flop, t flip lop disini dibuat dengan menggunakan d ff dan jk ff, dikarenakan t

ff tidak tersedia di proteu. ketika dijalankan

maka output yang dihasilkan akan

berubah" atau beralih".

Gambar (10.36): jika kita beri input logika 0 atau 1 maka outputnya berubah- ubah atau beralih

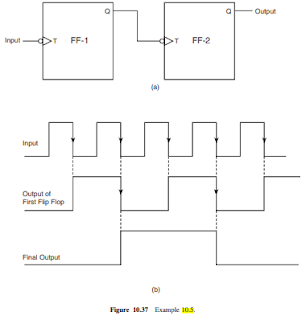

Gambar

10.37: pada gambar kali ini digunakan t flip

flop, t flip lop disini dibuat dengan menggunakan d ff dan jk ff, dikarenakan t

ff tidak tersedia di proteus. ketika dijalankan

maka output yang dihasilkan akan berubah" atau beralih" jika

kita menekan clock beberapa kali.

Gambar (10.24 a)

10.24 b

Gambar

10.26

Gambar (10.27)

Gambar (10.29 a)

Gambar

(10.29 b)

Gambar (10.31)

Gambar (10.32)

Gambar (10.36)

Contoh

10.3

Gambar

simbol sirkuit flip-flop yang diwakili oleh tabel fungsi Gbr. 10.31(a).

Solusi:

Tiga

entri pertama dari tabel fungsi menunjukkan bahwa flip-flop J-K memiliki PRESET

TINGGI aktif dan CLEAR input. Mengacu pada entri keempat dan kelima dari tabel

fungsi, ia memiliki Input J dan K. Baris ketujuh dari tabel fungsi

mengkonfirmasi hal ini. Output merespons positif (LOW-to-HIGH) tepi input jam.

Dengan demikian, flip-flop yang diwakili oleh tabel fungsi yang diberikan

adalah flip-flop yang dapat disetel, jelas, dan dipicu tepi positif dengan

PRESET TINGGI aktif dan CLEAR dan input LOW J dan K aktif. Gambar 10.31(b) menunjukkan

simbol sirkuit flip-flop yang diwakili dengan meja kebenaran ini.

Contoh

10.4

Bentuk

gelombang persegi 100 kHz dari Gbr. 10.32(a) diterapkan pada input jam

flip-flop yang ditunjukkan pada 10.32(b) dan (c). Jika output Q awalnya '0',

gambar bentuk gelombang output Q dalam dua kasus. Juga, tentukan frekuensi

output Q dalam dua kasus.

Solusi

Lihat

flip-flop Ara. 10.32(b). Q awalnya '0'. Hal ini membuat input J dan K

awalnya '1' dan '0' masing-masing. Dengan tepi trailing pertama input jam, Q

masuk ke status '1'. Dengan demikian, J dan K memperoleh status logika

masing-masing '0' dan '1'. Dengan tepi trailing berikutnya dari input jam, Q

masuk ke logika '0'. Proses ini berlanjut, dan Q secara bergantian menjadi '1'

dan '0'. Output Q bentuk gelombang untuk kasus ini ditampilkan dalam Gbr.

10.33(a). Dalam kasus flip-flop pada. 10.32 (c), J dan K masing-masing

berinisial '0' dan '1'. Dengan demikian, J aktif. Dengan tepi depan pertama

dari input jam, T dan oleh karena itu J pergi ke status logika '1'. Tepi

terdepan kedua memaksa Q untuk pergi ke logika '0' menyatakan seperti sekarang

adalah input K yang dalam keadaan logika '0' dan aktif. Sirkuit ini juga

berperilaku sama seperti sandal jepit Dari Gbr. 10.32(b). Output berjalan

secara bergantian ke status logika '0' dan '1'. Namun, transisi terjadi di tepi

depan input jam. Gambar 10.33(b) memperlihatkan Q bentuk gelombang output untuk

kasus ini. Frekuensi bentuk gelombang output Q dalam dua kasus sama dengan

setengah frekuensi input jam, untuk alasan yang jelas, dan karena itu 50 kHz.

Contoh

10.5

Lihat

pengaturan bertingkat dua flip-flop T di Gbr. 10.37(a). Menggambar bentuk

gelombang output Q untuk sinyal masukan yang diberikan. Jika periode waktu

sinyal input adalah 10 ms, temukan frekuensi sinyal keluaran? Jika, dalam

pengaturan flip-flop pada. 10.37(a), FF-2 dipicu tepi positif, gambar bentuk gelombang

output Q.

Solusi

Bentuk

gelombang output Q ditampilkan dalam Gbr. 10.37(b) bersama dengan output Q

FF-1. Keluaran dari pertama T flip-flop mengubah status untuk setiap

negatif-going edge dari bentuk gelombang jam input. Frekuensinya oleh karena

itu setengah dari frekuensi sinyal input. Output flip-flop pertama bertindak

sebagai input jam untuk flip-flop T kedua dalam pengaturan kaskade. Flip-flop

kedua juga, beralih untuk setiap tepi negatif dari bentuk gelombang muncul pada

inputnya. Output akhir dengan demikian memiliki frekuensi yang adalah

seperempat dari frekuensi sinyal input:

Sekarang

periode waktu sinyal input = 10 ms.

Oleh

karena itu, frekuensi = 100 kHz.

Frekuensi

sinyal output = 25 kHz.

Ketika flip-flop kedua

(FF-2) adalah yang dipicu tepi positif, itu akan merespons sisi bentuk

gelombang muncul pada input T-nya, yang merupakan bentuk gelombang yang muncul

pada output Q FF-1. Bentuk gelombang yang relevan dalam hal ini ditunjukkan

dalam Gbr. 10.38.

1.Apa itu

flip flop Jk

Jawab:

Flip flop JK merupakan flip flop yang paling ideal digunakan sebagai piranti

penyikpanan (memori). Flip flop JK digunakan pada setiap komputer digital

maupun piranti lainnya.

2.

Jelaskan dua jenis umpan balik pada flip flop JK!

Jawab:

Rangkaian dari flip flop terdiri dari rangkaian gerbang logika, seperti flip

flop lain. Tetapi, flip flop JK memilki keunikan tersendiri, yaitu pada

keluaran Q dan Q’ terdapat dua jenis umpan balik, dengan keluaran yang diumpan

balikkan kembali.

Ada dua

jenis umpan balik :

a. Umpan

Balik flip flop. Berfungsi supaya rangkaian gerbang logika yang berada di dalam

garis putus – putus FL dapat menahan sebuah data biner.

b. Umpan

balik Togel (Toggle). Umpan balik ini enyebabkan flip flop JK mengalami toggle.

1. Apa

manfaat dari penggunaan flip flop Jk, kecuali

a.

Pencacah frekuensi (frequency counter)

b.

Pembangkit ragam gelombang kotak simetri (symetri square wave form generator)

c.

Pencacah arus (current frequency)

d.

Pembagi frekuensi (frequency divider)

Jawab: c

2.

Dibawah ini merupakn gambar saat

a.

Keadaan toogle

b.

Keadaan reset

c.

Keadaan clear

d. Preset

Jawab: a (Ini terjadi saat masukan J dan K sama sama berniali 1 sehingga dihasilkan keadaan set dan reset yang terus bergantian)

HTML: disini

File Rangkaian 10.24-10.37: disini

Video Gambar (10.24 a):

Video Gambar (10.24 b):

Video Gambar (10.26 a

dan b):

Video Gambar (10.27):

Video Gambar (10.29 a):

Video Gambar (10.29 b):

Video Gambar (10.31):

Video Gambar (10.32):

Video Gambar (10.34): disini

Video Gambar (10.35): disini

Video Gambar (10.36):

Video Gambar

(10.37): disini

Datasheet Gerbang NAND:

Datasheet gerbang inverter: d

Datasheet D FF: disini

Datasheet JKFF: disini

Tidak ada komentar:

Posting Komentar